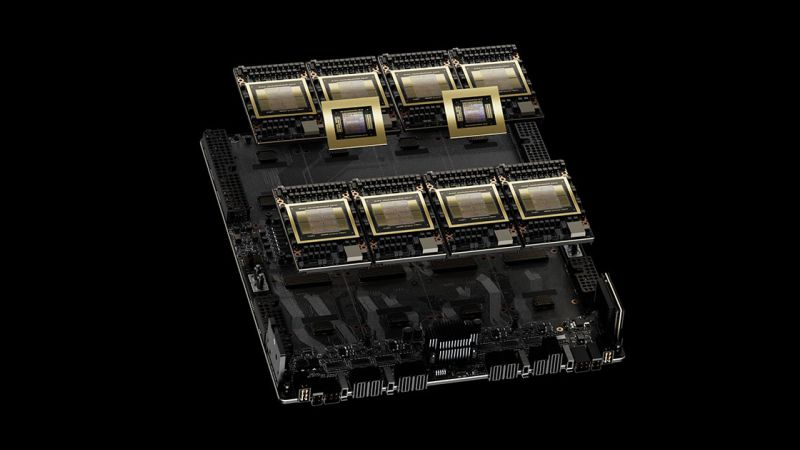

TSMC настаивает, что сможет освоить технологию A16 без оборудования для High-NA EUV

В конце апреля старший вице-президент TSMC Кевин Чжан (Kevin Zhang) уже признавался, что не считает целесообразным внедрять литографическое оборудование ASML с высоким значением числовой апертуры (High-NA) при производстве чипов по технологии A16, которая будет освоена во второй половине 2026 года. На этой неделе он повторил данный тезис, назвав соответствующее оборудование слишком дорогим.

«Мне нравятся возможности High-NA EUV, но не нравится ценник», — пояснил Кевин Чжан на технологическом симпозиуме в Нидерландах. Оборудование ASML нового поколения, о котором идёт речь, способно изготовить полупроводниковые элементы толщиной всего 8 нм, что в 1,7 раза меньше, чем получается при использовании литографических сканеров предыдущего поколения, но стоимость одной такой системы достигает $380 млн против примерно $216 млн у обычной.

Напомним, что ASML сейчас тестирует один из таких литографических сканеров для работы с High-NA EUV, второй установлен в исследовательском центре Intel в штате Орегон, а третий должна получить бельгийская Imec, которая является одним из партнёров японского консорциума Rapidus, рассчитывающего к 2027 году начать выпуск 2-нм продукции на территории Японии. Корпорация Intel будет экспериментировать с таким оборудованием в рамках технологии 18A, но в серийном производстве внедрит не ранее 2027 года, когда начнёт осваивать технологию Intel 14A. По слухам, Intel даже выкупила весь тираж литографических сканеров ASML нового поколения на этот год, чтобы обеспечить себя необходимым оборудованием.

Как уже отмечал ранее представитель TSMC, этот крупнейший тайваньский контрактный производитель чипов рассчитывает обойтись возможностями имеющегося оборудования. Кевин Чжан пояснил, что предприятия TSMC, на которых будет использоваться техпроцесс A16, могут быть приспособлены для дальнейшей установки оборудования с High-NA EUV, но когда оно потребуется в действительности, компания сказать не может. Сроки внедрения данной технологии на предприятиях TSMC будут определяться балансом технических характеристик выпускаемых чипов и экономическими факторами. Вся отрасль, по его словам, сталкивается с ростом затрат на строительство, оснащение и эксплуатацию предприятий по выпуску чипов.

Источник